集成電路IC后端設(shè)計(jì)的關(guān)鍵步驟

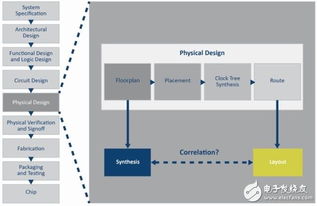

集成電路(IC)后端設(shè)計(jì)是芯片設(shè)計(jì)流程中的關(guān)鍵環(huán)節(jié),主要負(fù)責(zé)將前端邏輯設(shè)計(jì)轉(zhuǎn)化為可制造的物理布局。其核心目標(biāo)是確保芯片滿足時(shí)序、功耗和面積等性能指標(biāo)的實(shí)現(xiàn)高良率的制造。后端設(shè)計(jì)通常包括以下主要步驟:

- 邏輯綜合:將前端設(shè)計(jì)的寄存器傳輸級(RTL)代碼轉(zhuǎn)換為門級網(wǎng)表,同時(shí)考慮工藝庫、時(shí)序約束和功耗要求。綜合過程優(yōu)化電路結(jié)構(gòu),確保邏輯功能正確并滿足初步性能目標(biāo)。

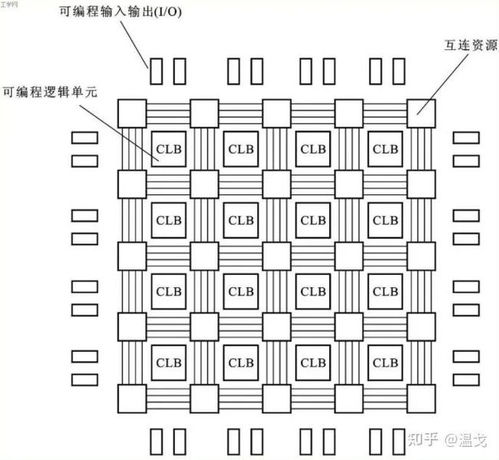

- 布局規(guī)劃:確定芯片上各個(gè)功能模塊的位置和形狀,包括電源網(wǎng)絡(luò)、I/O引腳和硬核的擺放。布局規(guī)劃直接影響布線擁塞、時(shí)序和散熱,是后端設(shè)計(jì)的基礎(chǔ)。

- 電源規(guī)劃:設(shè)計(jì)電源分布網(wǎng)絡(luò)(PDN),確保芯片各區(qū)域獲得穩(wěn)定供電。這包括電源環(huán)、電源帶和去耦電容的布局,以降低電壓降和電遷移風(fēng)險(xiǎn)。

- 布局:將標(biāo)準(zhǔn)單元和宏模塊放置在芯片的特定位置,優(yōu)化連線長度和時(shí)序。布局工具通過算法最小化延遲和面積,同時(shí)考慮制造規(guī)則。

- 時(shí)鐘樹綜合:構(gòu)建時(shí)鐘分布網(wǎng)絡(luò),確保時(shí)鐘信號同步到達(dá)所有時(shí)序單元。時(shí)鐘樹設(shè)計(jì)需平衡偏斜、功耗和面積,通常采用平衡樹結(jié)構(gòu)(如H樹或網(wǎng)格)。

- 布線:連接所有單元和模塊的物理線路,包括全局布線和詳細(xì)布線。布線需避免天線效應(yīng)、串?dāng)_和電遷移問題,同時(shí)滿足設(shè)計(jì)規(guī)則檢查(DRC)要求。

- 時(shí)序和功耗分析:通過靜態(tài)時(shí)序分析(STA)和功耗模擬驗(yàn)證設(shè)計(jì)是否滿足時(shí)序約束和功耗預(yù)算。必要時(shí)進(jìn)行優(yōu)化,如插入緩沖器或調(diào)整單元尺寸。

- 物理驗(yàn)證:執(zhí)行設(shè)計(jì)規(guī)則檢查(DRC)、版圖與原理圖對照(LVS)和電氣規(guī)則檢查(ERC),確保版圖符合代工廠的制造標(biāo)準(zhǔn)和電氣特性。

- 簽核:最終驗(yàn)證設(shè)計(jì)的所有指標(biāo),包括時(shí)序、信號完整性和功耗。簽核通過后,生成GDSII文件交付制造。

后端設(shè)計(jì)是IC實(shí)現(xiàn)的核心,其成功依賴于EDA工具、工藝庫和設(shè)計(jì)經(jīng)驗(yàn)的緊密結(jié)合。隨著工藝節(jié)點(diǎn)不斷縮小,后端設(shè)計(jì)面臨更多挑戰(zhàn),如寄生效應(yīng)、熱管理和可制造性設(shè)計(jì)(DFM),需要持續(xù)創(chuàng)新和優(yōu)化。

如若轉(zhuǎn)載,請注明出處:http://www.10brand.org.cn/product/46.html

更新時(shí)間:2026-01-09 16:35:35