集成電路設(shè)計 從概念到現(xiàn)實的精密藝術(shù)

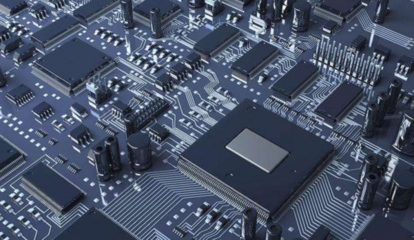

集成電路設(shè)計是現(xiàn)代電子工業(yè)的核心技術(shù)之一,它涉及將數(shù)以億計的晶體管、電阻、電容等電子元件集成在一塊微小的半導(dǎo)體芯片上。隨著摩爾定律的持續(xù)推進,集成電路設(shè)計已經(jīng)發(fā)展成為一門融合電子工程、計算機科學、物理學和材料學的綜合性學科。

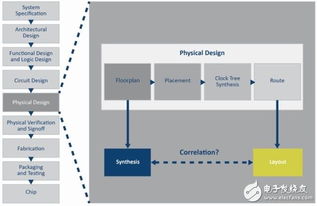

集成電路設(shè)計流程通常包括以下幾個關(guān)鍵階段:

1. 系統(tǒng)架構(gòu)設(shè)計

設(shè)計團隊首先需要明確芯片的功能需求和技術(shù)指標,確定整體架構(gòu)方案。這個階段需要考慮處理器的核心數(shù)量、內(nèi)存架構(gòu)、接口標準等關(guān)鍵參數(shù),制定出滿足市場需求的芯片規(guī)格。

2. 邏輯設(shè)計

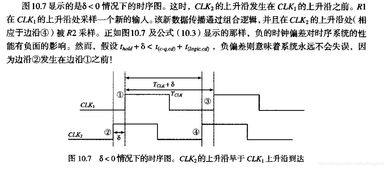

在架構(gòu)確定后,工程師使用硬件描述語言(如Verilog或VHDL)進行邏輯設(shè)計。這個階段將功能需求轉(zhuǎn)化為具體的數(shù)字邏輯電路,包括組合邏輯和時序邏輯的設(shè)計,確保電路能夠正確實現(xiàn)預(yù)定功能。

3. 電路設(shè)計

邏輯設(shè)計完成后,進入晶體管級的電路設(shè)計。設(shè)計人員需要確定每個邏輯門的具體實現(xiàn)方式,考慮延遲、功耗、面積等關(guān)鍵指標。模擬電路和混合信號電路的設(shè)計也在此階段完成。

4. 物理設(shè)計

這是最復(fù)雜的階段,涉及布局布線工作。工程師需要將電路元件精確地放置在芯片上,并用金屬線連接起來。這個過程需要考慮信號完整性、時序收斂、功耗分布、散熱等多個因素。現(xiàn)代芯片的布線層數(shù)可達十幾層,布線總長度可達數(shù)公里。

5. 驗證與測試

設(shè)計完成后需要進行嚴格的驗證,包括功能驗證、時序驗證、物理驗證等。只有通過所有驗證環(huán)節(jié)的設(shè)計才能進入制造階段。芯片制造出來后還需要進行實際的測試,確保產(chǎn)品符合設(shè)計要求。

集成電路設(shè)計面臨著諸多挑戰(zhàn):

- 功耗管理:隨著集成度提高,功耗密度不斷上升

- 信號完整性:高頻信號在微小尺寸下易受干擾

- 制造變異:納米級工藝下的工藝偏差影響電路性能

- 設(shè)計復(fù)雜性:數(shù)十億晶體管的設(shè)計需要高效的EDA工具支持

隨著人工智能、物聯(lián)網(wǎng)、5G等新技術(shù)的發(fā)展,集成電路設(shè)計正在向更智能化、專業(yè)化的方向發(fā)展。異構(gòu)集成、三維集成電路、神經(jīng)形態(tài)計算等新興技術(shù)為集成電路設(shè)計開辟了新的發(fā)展空間。

集成電路設(shè)計是一門精密而復(fù)雜的工程技術(shù),它不僅是技術(shù)創(chuàng)新的體現(xiàn),更是推動整個信息產(chǎn)業(yè)發(fā)展的核心動力。

如若轉(zhuǎn)載,請注明出處:http://www.10brand.org.cn/product/27.html

更新時間:2026-01-09 21:44:55